# Comparison of Physical and Software-Implemented Fault Injection Techniques

Jean Arlat, *Member*, *IEEE*, Yves Crouzet, Johan Karlsson, *Member*, *IEEE*, Peter Folkesson, *Member*, *IEEE*, Emmerich Fuchs, *Member*, *IEEE Computer Society*, and Günther H. Leber, *Member*, *IEEE*

**Abstract**—This paper addresses the issue of characterizing the respective impact of fault injection techniques. Three physical techniques and one software-implemented technique that have been used to assess the fault tolerance features of the MARS fault-tolerant distributed real-time system are compared and analyzed. After a short summary of the fault tolerance features of the MARS architecture and especially of the error detection mechanisms that were used to compare the erroneous behaviors induced by the fault injection techniques considered, we describe the common distributed testbed and test scenario implemented to perform a coherent set of fault injection campaigns. The main features of the four fault injection techniques considered are then briefly described and the results obtained are finally presented and discussed. Emphasis is put on the analysis of the specific impact and merit of each injection technique.

Index Terms—Fault injection techniques, experimental assessment, fault-tolerant computing, error detection coverage.

# **1** INTRODUCTION

The dependability assessment of a fault-tolerant computer system is a complex task that requires the use of different levels of evaluation approaches and related tools. In complement to other possible approaches such as proving or analytical modeling whose applicability and accuracy are significantly restricted in the case of complex systems, *fault injection* has long been recognized to be particularly attractive and useful. Indeed, by speeding up the occurrence of errors and failures, fault injection is, in fact, a method for *testing* the fault tolerance mechanisms with respect to a specific set of inputs they are meant to cope with: *the faults*. Fault injection can be applied either on a simulation model of the target faulttolerant system or on a hardware-and-software implementation (e.g., see [1], [2], [3], [4]).

Clearly, simulation-based fault injection is desirable as it can provide early checks in the design process of fault tolerance mechanisms (e.g., see [5]). Nevertheless, it is worth noting that fault injection on a prototype featuring the actual interactions between the hardware and software dimensions of the fault tolerance mechanisms supplies a more realistic and necessary complement to validate their implementation in a fault-tolerant system.

- J. Arlat and Y. Crouzet are with LAAS-CNRS, 7, Avenue du Colonel Roche, 31077 Toulouse Cedex 4, France.

E-mail: {Jean.Arlat, Yves.Crouzet)@laas.fr.

- J. Karlsson and P. Folkesson are with the Department of Computer Engineering, Chalmers University of Technology, SE-412 96 Goteborg, Sweden. E-mail: {johan, peterf]@ce.chalmers.se.

- E. Fuchs was with the Vienna University of Technology. He is now with DECOMSYS-Dependable Computer Systems, Stumpergasse 48/14, A-1060 Wien, Austria. E-mail: fuchs@decomsys.com.

- G.H. Leber was with the Vienna University of Technology. He is now with Adcon Telemetry AG, Inkustraße 24, A-3400 Klosterneuburg, Austria. E-mail: guenther.leber@ieee.org.

Manuscript received 14 Feb. 2000; revised 12 Feb. 2002; accepted 24 Feb. 2003.

For information on obtaining reprints of this article, please send e-mail to: tc@computer.org, and reference IEEECS Log Number 111469.

Initially, most studies related to the application of fault injection on a prototype of a fault-tolerant system relied on physical fault injection ( $\Phi$ FI, for short), i.e., the introduction of faults through the hardware layer of the target system (e.g., see [6]). A trend favoring the injection of errors through the software layer for simulating physical faults (i.e., software-implemented fault injection—SWIFI for short) has emerged (e.g., see [7], [8], [9], [10], [11]). Such an approach facilitates the application of fault injection by overcoming several problems associated with  $\Phi$ FI techniques (such as controllability, repeatability, etc.). Moreover, recent studies have shown that SWIFI was also able to emulate some types of software faults (e.g., see [12]).

Nevertheless, in spite of the difficulties in developing support environments and conducting experiments,  $\Phi$ FI techniques enable real faults to be injected in a very close representation of the target system especially without any alteration to the software being executed. The large body of works concerning  $\Phi$ FI used widely different techniques and/or were applied to distinct target systems. This significantly hampers the possibility to identify the difficulties/benefits associated with each fault injection technique and to analyze the results obtained.

Thus, more experimental work is needed to better establish the relationship and differences between the fault injection techniques that are available to help the designers in assessing the dependability and fault tolerance properties of a computer system. In particular, one key concern that is often related to fault injection-based experiments is usually termed *fault representativeness*, i.e., the plausibility of the supported fault model with respect to actual faults. In this paper, we advocate that the study of the impact and consequences of an injected fault (i.e., the error propagated) offers a more pragmatic and sensible means to address the representativeness issue. Accordingly, we distinguish between two categories of approaches, depending on whether the analysis concerns the erroneous behaviors provoked by 1) some specific fault injection technique with respect to a set of real faults or 2) the application of several fault injection techniques (most of the time in previous studies only two techniques were considered).

Clearly, in principle, the first approach is more desirable and convincing for assessing the accuracy of the behaviors induced by the fault injection techniques. However, it is not always easy to gather a large amount of objective data on behaviors caused by real faults to support such an analysis. Typical examples of related studies include the comparison of the impact of real faults with respect to 1) extensive data and code corruptions [13], 2) elementary source code mutations [14], or 3) application of the SWIFI technique [12].

For what concerns the second approach, the comparison of several fault injection techniques provides only an indirect means for assessing their representativeness; nevertheless, such an approach is well suited to obtaining extensive error data sets from which useful insights can be derived. Should the experiments using different fault injection techniques lead to similar behaviors, then the techniques can be considered as "equivalent" and, thus, the one that exhibits the most suitable practical properties (e.g., reachability, controllability, reproducibility, intrusiveness, etc.) should be preferred. However, if different behaviors are observed, then the techniques are rather complementary. Such an insight is very much helpful in light of the work devoted to developing dependability benchmarks (e.g., see [11], [15], [16]),<sup>1</sup> in particular to substantiate which kind of relevant "faultload" should be considered for such benchmarks. Among the related studies, we would like to refer to the works reported in [10], [17], [18], [19], [20], [21], [22] that addressed most of the currently available fault injection techniques, including simulation-based techniques, ΦFI techniques, SWIFI techniques, and, also, the recently introduced scan chain-implemented fault injection technique, e.g., see [23], that builds upon the testabilitysupport capabilities featured by many modern VLSI devices.

These studies showed that some fault injection techniques matched some real faults rather well and also that some were found to be quite equivalent, while others were identified as rather complementary. Accordingly, more experimental work and related analyses are needed to better understand the underlying error creation and propagation mechanisms.

This paper is intended to contribute to this effort along the lines of the second approach described earlier, by studying whether the application of four distinct fault injection techniques had the same impact on a specific prototype of a fault-tolerant real-time system. Three  $\Phi$ FI techniques, namely, heavy-ion radiation, pin-level injection, and electromagnetic interferences, as well as a preruntime SWIFI technique (at the machine code level) were considered. In each case, the target fault-tolerant system was a prototype of the MARS (MAintainable Real-time System) distributed architecture developed at the Vienna University of Technology [24]. It is worth noting that this conceptual prototype architecture has evolved to become the Time Triggered Protocol and Architecture (also known as TTP and TTA), e.g., see [25].

The initial motivation for our work was to assess the *coverage* of the "fail-silent" assumption [26] and also to evaluate the respective efficiency (i.e., the detection *coverage*) of the various built-in error detection mechanisms (EDMs) aimed at supporting the fail silence property for the distributed computing nodes of the MARS architecture. The results obtained were previously reported in [27], for what concerns the experiments related to the three  $\Phi$ FI techniques, and in [28] for the SWIFI experiments.

It is worth noting that, in order to carry out all the fault injection experiments on a consistent basis, we used the same distributed testbed architecture featuring five MARS nodes and a common test scenario. Accordingly, it was easy to extend our analyses toward the comparison of the erroneous behaviors provoked by the considered fault injection techniques. A preliminary comparative study of the coverage provided by the EDMs and of *fail silence* property achieved with respect to the  $\Phi$ FI and SWIFI techniques was reported in [29]. This paper significantly extends these results and provides some insights to help understand 1) the differences between the errors provoked by the  $\Phi$ FI techniques and 2) to what extent SWIFI can simulate the consequences of faults injected by the physical techniques.

To the best of our knowledge, this study is rather unique, both in providing such a comprehensive comparison of several fault injection techniques and in relying on a wellcontrolled experimental context that allowed for drawing meaningful comparisons. Indeed, the assessment of the fault injection techniques is supported by using the EDMs in a MARS node as "observers" to characterize the erroneous behaviors induced by the faults injected by the techniques considered. The remaining part of this paper is composed of seven sections. Section 2 highlights the fault tolerance features of MARS, focusing on the EDMs built in each MARS node. Section 3 then presents the overall framework supporting the experimental assessment. It describes the common test scenario and testbed architecture being used for carrying out the fault injection experiments, as well as the failure predicates defined for characterizing the behavior of the target system in the presence of injected faults. Section 4 briefly describes the fault injection techniques considered. Some major experimental results concerning the target fault-tolerant system are presented and discussed in Section 5. Section 6 focuses on the analysis on the respective impact of the fault injection techniques considered. Section 7 complements this analysis by considering additional properties that also characterize the application of the fault injection techniques. Finally, Section 8 concludes the paper.

# 2 THE MARS ARCHITECTURE AND ERROR DETECTION MECHANISMS

This section summarizes the main fault tolerance features of the MARS architecture [24]. Fault tolerance issues at

<sup>1.</sup> Recent related efforts also include the SIG on Dependability Benchmarking established by IFIP WG 10.4 (http://www.dependability. org/wg10.4/SIGDeB) and the European Project on Dependability Benchmarking—DBench-Project IST 2000-25425 (http://www.laas.fr/dbench).

system-level are discussed first, then the structure of a special-purpose processing node designed to support these features in an optimal way is briefly described. Finally, special attention is paid to the identification and characterization of the error detection mechanisms (EDMs) built-in into a MARS node.

# 2.1 Fault Tolerance

Fault tolerance in MARS is based on "fail-silent" nodes operating in active redundancy and on sending duplicate messages on two redundant real-time buses. *Fail silence* is intended to describe the behavior of a computer that fails "cleanly" by just stopping to send messages in case a failure occurs [30]. Up to three processing nodes can execute identical software, thus forming a Fault-Tolerant Unit (FTU).

To achieve a deterministic timing behavior even in the presence of faults, the MARS system uses active redundancy for all processing and communication activities: Each process is executed simultaneously at all nodes of an FTU and each message is transmitted quasi-simultaneously on each of the broadcast channels. Due to the fail silence property, the results of all three nodes of an FTU are assumed to be correct and may be used interchangeably. Since only two nodes are needed to tolerate a single failure of a fail-silent node (i.e., the loss of a message), the optional third node, the shadow node, does not transmit any message on the real-time network as long as both active nodes are operational. Only if an active node fails does the shadow node immediately start to transmit its results, thus restoring the initial degree of redundancy. A precise global time is maintained by a distributed fault-tolerant clock synchronization algorithm [24].

MARS uses a two-layered mechanism for fault tolerance. Due to the fail silence assumption supporting the design of the node, the top layer (system layer) need not care about erroneous data; it only has to provide enough redundancy to tolerate (silent) failures of parts of the system. Indeed, the bottom layer (node layer) is responsible for error detection and error confinement (i.e., it ensures the fail silence property of the node: After the detection of an error, a reset of the node is performed). In the context of this paper, a MARS node is said to be fail-silent if it only sends: 1) correct messages, 2) no messages, or 3) detectably wrong messages, which can be discarded by each nonfaulty receiver. An additional feature in the MARS architecture is that a node is only allowed to send a message at fixed time intervals according to a TDMA media access strategy.

#### 2.2 Structure of the Processing Node

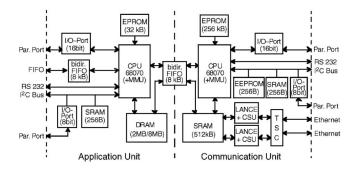

This study uses a single-board implementation of the MARS nodes. Each node consists of two independent processing units: the application unit and the communication unit (Fig. 1). Each unit is based on a 68070 CPU [31], that features a memory management unit (MMU). The application unit also contains a dynamic RAM and two bidirectional FIFOs, one of which serves as an interface to external add-on hardware, the other one connecting the application unit to the communication unit. Additional hardware for the communication unit is comprised of a Static RAM, two ethernet controllers (LANCEs), each coupled to a Clock Synchronization Unit (CSU) for

Fig. 1. Block diagram of the processor board.

maintaining a global time base, and a Time Slice Controller (TSC) for controlling access to the system bus.

Whenever an error is detected, the subsequent error processing activity of the node is to save the error information into nonvolatile memory and then turn itself off. Upon restart, the node writes its previously saved error information to two serial ports (one for each unit), from where it can be read for the purpose of diagnosis. This feature was exploited in the context of this study to precisely monitor and characterize the consequence of the injected faults. More details on MARS features and on the architecture of the processing nodes can be found in [24].

Three levels of error detection mechanisms (EDMs) are implemented in the MARS nodes: 1) the hardware EDMs, 2) the system software EDMs implemented in the operating system [24] and support software (i.e., the Modula/R compiler) [32], and 3) the application-level (end-to-end) EDMs at the highest level. They are respectively described in the following paragraphs.

#### 2.3 Hardware Error Detection Mechanisms

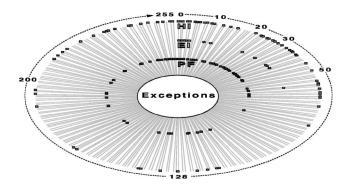

Whenever an error is detected by one of the hardware EDMs, in general, an *exception* is raised and the two CPUs will then wait for a reset issued by a watchdog timer. This watchdog timer is the only device that may cause a reset of all devices, including the CPUs.

Two main categories of hardware EDMs can be distinguished: the built-in mechanisms of the CPUs and those provided by special hardware on the processing board. In addition, faults can also trigger "unexpected" exceptions (i.e., neither the EDMs built into the CPUs nor the mechanisms provided by special hardware are mapped to these exceptions).

The EDMs built into the CPUs are: bus error, address error, illegal op-code, privilege violation, zero-divide, stack format error, noninitialized vector interrupt, and spurious interrupt. These errors cause the processor to jump to the appropriate exception handling routines, which save the error state to the nonvolatile memory and then reset the node.

The following errors are detected by mechanisms implemented by special hardware on the node: silent shutdown of the CPU of the communication unit, power failure, parity error, FIFO over/underflow, access to physically nonexisting memory, write access to the realtime network at an illegal point in time (monitored by the TSC), error of an external device, and error of the other unit. We globally call these "NMI mechanisms" as they raise a Non-Maskable Interrupt (a specific exception number) when an error is detected. An NMI leads to the same error handling as EDMs built into the CPUs and can only be cleared by resetting the node, which is carried out by the watchdog timer.

#### 2.4 System Software Error Detection Mechanisms

These mechanisms consist of EDMs implemented by the operating system or special system tasks; they include:

- assertions built into the operating system (OS), such as integrity checks on data or processing time overflow,

- mechanisms inserted by the compiler (i.e., Compiler Generated Run-Time Assertions—CGRTA) to implement concurrent checks, such as value range overflow of a variable and loop iteration bound overflow.

When an error is detected by any of these mechanisms, a "trap" instruction is executed that leads to a node reset.

#### 2.5 End-to-End Error Detection Mechanisms

These mechanisms include end-to-end checksums for message data and multiple (basically, double) execution of tasks.

The end-to-end checksums are used to detect the mutilation of message data exchanged between two nodes of an FTU and are therefore used by the receiving task for extending the fail silence property of the MARS nodes.

Double execution of tasks in time redundancy can detect errors caused by transient faults that cause different output data of the two instances of the task. Combined with the concept of message checksums, task execution in time redundancy forms the highest level in the hierarchy of the error detection mechanisms. These mechanisms also trigger the execution of a trap instruction, which causes a reset of the node.

# **3** OVERVIEW OF THE EXPERIMENTAL FRAMEWORK

In this section, we first present the common testbed set-up and workload implemented at all sites for carrying out the experiments. Then, we precisely define the failure predicates considered during the fault injection experiments.

#### 3.1 The Experimental Testbed and Workload

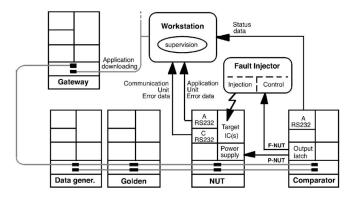

As depicted in Fig. 2, the common distributed testbed that is supporting the fault injection experiments features five MARS nodes.

The node under test (NUT, for short) is the node subject to the injection of a fault during each experiment run. Another node (*golden* node) serves as a reference and a third node (*comparator* node) is used to compare the messages sent by the two previous nodes. When a discrepancy is observed by the comparator node (fail silence violation) or the NUT detects an error, the NUT is declared to be failed and then shut down by the comparator node to clear all error conditions for the subsequent experiment run. After some time, power is reinstalled and the NUT is reloaded for the next experiment run. The *data generation* node simulates the data corresponding to the real-time application that is

Fig. 2. The testbed architecture featuring five MARS nodes.

being used to activate the NUT and the golden node during each fault injection experiment.

The application is taken from the rolling ball demonstration [33]: A ball is kept rolling along a circular path on a tiltable plane by controlling the two horizontal axes of the plane by servo motors and observing the position of the ball with a video camera. However, the tiltable plane and the camera are not present in the set-up used in the fault injection experiments; instead, the data from the camera is simulated by a data generation task running on the *data generation* node. The task provides the nominal and actual values of the position, speed, and acceleration of the ball.

A fifth node is included that serves as a *gateway* between a local area network (LAN) and the MARS network. It is required for loading the entire application and for reloading the NUT. A host computer (Unix workstation) connected to the LAN is used for supervising the experiments, i.e., reloading failed nodes and collecting data from each experiment run for further analysis.

Fig. 2 also depicts the specific interactions with the  $\Phi$ FI devices. The experiments are managed by the workstation and controlled by the comparator node. When the comparator node detects an error, it reports the error type to the workstation and turns off the power to the NUT with the signal P-NUT. Signal F-NUT is used to discontinue fault injection.<sup>2</sup> Then, the NUT is powered-up again and restarted. Upon restart, the memorized error data is sent to the workstation via two serial lines (one for each processing unit).<sup>3</sup> Once the NUT has been restarted, the workstation immediately initiates the downloading of the application via the gateway node. When the application has been restarted, the comparator node enables fault injection (signal F-NUT) and a new experiment run begins.

Finally, it is worth noting that the experimental set-up is based on the assumption that the nodes are *replica determinate* (both in value and in time domains), i.e., if provided with the same input data, replicated nodes deliver identical outputs in an identical order within a specified time interval. In particular, extensive runs without fault injection of the rolling-ball target application have demonstrated that the MARS prototype architecture supported

<sup>2.</sup> Such a direct control on the injected fault is not possible in the case of the software-implemented fault injection technique used (see Section 4.4).

<sup>3.</sup> If the error was not detected by the NUT itself, then the node has no error information available and sends only a status message.

TABLE 1 The Basic Predicates

| Cold Start ( <i>CS</i> )     | Cold start (power on) of the NUT is performed after every experiment run, except when a system failure occurred.                                                                                                                                                                   |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Warm Start ( <i>WS</i> )     | Warm start (reset) of the NUT caused by the detection of i) an error by the node's EDMs ( <i>Internal WS</i> ) or, ii) an incoming or outgoing link failure by means of the top layer of the fault tolerance mechanism, i.e., the membership protocol [35] ( <i>External WS</i> ). |

| Message Loss (ML)            | One message (or more) from NUT was lost (i.e., not received by the comparator node).                                                                                                                                                                                               |

| Message Mismatch (MM)        | Reception by the comparator node of differing messages from golden node and NUT.                                                                                                                                                                                                   |

| System Failure ( <i>SF</i> ) | Failure of either the golden, data generation, or comparator nodes.                                                                                                                                                                                                                |

this property. Besides its interest for handling replicated entities in real-time fault-tolerant systems (e.g., see [34]), such a feature proved very useful in the context of the fault injection experiments so that the faulty behaviors between the testbed instances used for supporting each fault injection technique could be meaningfully compared.

# 3.2 The Failure Predicates

Four failure types can be distinguished for the NUT:

- The EDMs detect an error and the node stops sending messages on the MARS bus; then, the node stores the error condition into a nonvolatile memory and resets itself by means of the watchdog timer.

- 2. The node fails to deliver the expected application message(s) for one or several application cycles, but no error is detected by the EDMs.

- 3. The node delivers a syntactically correct message with erroneous content. This is a fail silence violation in the value domain, which is recognized as a mismatch between the messages sent by the NUT and the golden node.

- 4. The node sends a message at an illegal point in time and thus disturbs the traffic on the MARS bus. This is a fail silence violation in the time domain.

On every restart, the NUT writes its previously saved error data, if available (i.e., if an error was detected by the EDMs) and data about its state to two serial ports, where it can be read and stored for further processing. From these data, five predicates (events) can be derived (Table 1).

The Cold Start (CS) predicate characterizes the end of each data set. The other four predicates characterize four failure types. The assertion (occurrence) of the Warm Start (WS) predicate in the data corresponds to the normal case when the node under test detects the error (failure type 1). The assertion of ML corresponds to a Message Loss (failure type 2); this behavior is not a fail silence violation because no erroneous data is sent, but it cannot be regarded as normal operation. Irrespective of the other events, the assertion of a Message Mismatch (MM) (failure type 3) corresponds to a fail silence violation (in the data domain). There are two ways in which a System Failure (SF) may occur: 1) A fail silence violation in the time domain (failure type 4) affects the operation of the other nodes, or 2) another node than NUT experiences a real hardware failure during the experiments. Although, no SF-type failures were observed in the conducted experiments, this failure event is described for the sake of completeness.

Given these failure types, the number of fail silence (*FS*) violations can be counted as:

$$\#$$

FS Viol. =  $\#$ Exp. MM +  $\#$ Exp. SF,

where # *Exp. X* counts the number of experiments where an *X*-type failure was diagnosed (i.e., predicate *X* was asserted).

# 4 THE FAULT INJECTION TECHNIQUES

In this section, we briefly present the main features of the four fault injection techniques applied for the experimental assessment of the MARS system.

#### 4.1 Heavy-Ion Radiation

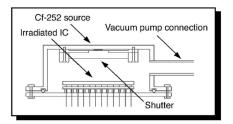

The fault injection experiments with heavy-ion radiation (HI, for short) were carried out at Chalmers University of Technology in Göteborg, Sweden. Heavy-ion radiation from a Californium-252 source can be used to inject single event upsets, i.e., bit-flips at internal locations in integrated circuits (ICs) using a miniature vacuum chamber. Fig. 3 depicts the cross-sectional view of the miniature vacuum chamber. The pins of the target IC are extended through the bottom plate of the vacuum chamber so that the chamber with the circuit can be directly plugged into the socket of the circuit under test. The vacuum chamber contains an electrically controlled shutter, which is used to shield the circuit under test from radiation during bootstrapping.

A major feature of the heavy-ion fault injection technique is that faults can be injected into VLSI circuits at locations which are difficult (and mostly impossible) to reach by other techniques. The transient faults produced are also reasonably well spread at random locations within an IC as there are many sensitive memory elements in most VLSI circuits. As device feature sizes of integrated circuits are shrinking, radiation induced bit-flips, also known as soft errors, are becoming an increasingly important source of

Fig. 4. Principle of pin-forcing fault injection.

failures in computer systems, e.g., see [36], [37]. While soft errors are caused mainly by heavy ions in space, at ground level and airplane flight altitudes, they are instead caused by atmospheric neutrons [38].

Although the heavy-ions emitted from Cf-252 do not provide a perfect imitation of the impact of either heavy ions in space or neutron radiation on earth (e.g., with respect to the ratio between multiple and single bit upsets), the method provides a practical approach to evaluating the effectiveness of error detection and recovery mechanisms with respect to soft errors. Exposing circuits to neutron radiation is less practical since it involves placing the tested system in a room with concrete shielding [39].

For the 68070 CPU, the heavy-ions from Cf-252 mainly provoke single bit upsets; the percentage of multiple bit errors induced in the main registers was found to be less than 1 percent in the experiments reported in [40]. The heavy-ion method has been previously used to evaluate several hardware and software-implemented error detection mechanisms for the MC6809E microprocessor. A comprehensive description of these experiments using the heavy-ion fault injection technique is given in [2].

# 4.2 Pin-Level Injection

Pin-level fault injection, i.e., the injection of faults directly on the pins of the ICs of a prototype, probably was the most widely applied physical fault injection technique. Some flexible tools supporting general features have been developed (e.g., see the test facility used on the MAFT system [41], MESSALINE [1], RIFLE [42], or AFIT [43]).

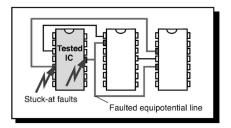

The experiments with the pin-level fault injection technique were conducted at LAAS-CNRS, in Toulouse, France, using MESSALINE. Fig. 4 depicts the principle of the pin-forcing technique (PF, for short) that was used. In the case of pin-forcing, the injected fault is directly applied on the pin(s) of the target IC.

It is noteworthy that the pins of the ICs connected, by means of an equipotential line, to an injected pin are faulted as well. Accordingly, to simplify the accessibility to the pins of the microprocessor, the target ICs were mainly the buffer ICs directly connected to it. The supported fault models include temporary stuck-at faults affecting single or multiple pins. Indeed, temporary faults injected on the pins of the ICs can simulate the consequences of internal faults on the pins of the faulted IC(s).

The tool already contributed to the experimental assessment of two fault-tolerant systems: 1) for testing the diagnosis features of a computerized railway interlocking system and 2) for evaluating the fail silence property of the Delta-4 fault-tolerant architecture [1], [30].

Fig. 5. Application of electromagnetic interferences.

#### 4.3 Electromagnetic Interferences

Electromagnetic interferences (EI) are common disturbances in automotive vehicles, trains, airplanes, or industrial plants. Such a technique is widely used to stress digital equipment.

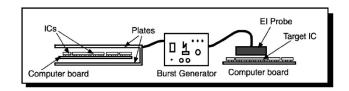

The EI experiments were carried out at the Technical University of Vienna, Austria. Thanks to the use of a commercial burst generator, this technique is easy to implement. Two different forms of application of this technique were considered (Fig. 5).

In the first form, the single computer board of the NUT was mounted between two metal plates connected to the burst generator. In this way, the entire node was affected by the generated bursts. Because the Ethernet transceivers turned out to be more sensitive to the bursts than the node under test itself, a second configuration was set up which used a special probe that was directly placed on top of the target circuit. In this way, the generated bursts affected only the target circuit (and some other circuits located near the probe).

# 4.4 Software-Implemented Fault Injection

Software-implemented fault injection (SWIFI) provides a low cost and easy-to-control alternative to the three physical fault injection techniques previously described that require special hardware instrumentation and interfaces to the target system. SWIFI is usually achieved by changing the contents of memory or registers based on specified fault models to emulate the consequences of hardware faults or to inject software faults (e.g., see [9]).

For these experiments, an alternative approach was selected that injected the faults at preruntime at the machine code level and loaded the mutilated application (code segment or data segment) to the target system afterward. Three main reasons led us to select such an approach [28]:

- 1. The intrusiveness is reduced to a minimum since faults are injected only into the application software (no additional code, which could probably alter the behavior of the application software, is needed, i.e., fault injection is transparent to the application),

- 2. Fault injection at the machine code level is capable of injecting faults which cannot be injected at higher levels by using source code mutations (e.g., see [44], [45]).

- 3. Preruntime injection smoothly integrates with the application development process because applications are developed, configured, allocated, and scheduled offline on a host computer and loaded onto the target system afterward.

SWIFI experiments started at the Vienna University of Technology, Austria, and continued at the Research and

| Configuration # | Message Checksum | Execution | Acronym |

|-----------------|------------------|-----------|---------|

| 1               | No               | Single    | NOAM    |

| 2               | Yes              | Single    | SEMC    |

| 3               | Yes              | Double    | DEMC    |

| 4               | Yes              | Triple    | TEMC    |

TABLE 2 **Experimental Configurations**

Explanation of the Acronyms Used to Describe the Results

| Acronym and Entry       | Explanation                                                                            |

|-------------------------|----------------------------------------------------------------------------------------|

| CPU                     | CPU-internal EDMs                                                                      |

| UEE                     | Unexpected exceptions (i.e., without dedicated error handler)                          |

| NMI                     | Non-maskable interrupts generated by additional circuits of the NUT                    |

| OS                      | Checks and assertions coded in the operating system software                           |

| CGRTA                   | Compiler generated run-time assertions                                                 |

| Double exec.            | Time redundant (Double) execution of application tasks                                 |

| Checksum                | Checksum of message exchanged                                                          |

| Other unit              | The error information was provided by the other unit (not the faulted unit) of the NUT |

| No error info.          | None of the two units of the NUT provided valid error information                      |

| Triple execution        | Time redundant (Triple) execution of application tasks*                                |

| IM Loss                 | Intermittent loss of application message <sup>0</sup>                                  |

| No Reply                | The injected fault(s) had no observable effect <sup>0</sup>                            |

| Fail silence violations | Mismatch between the NUT and the golden node (as observed by the comparator node)      |

|                         | * Heavy-ion injection, only <sup>◊</sup> SWIFI, only                                   |

Technology Institute of Daimler Benz AG (now Daimler-Chrysler) in Berlin, Germany [46]. The way the fault injection experiments are conducted overview of the acronyms and entries found in the subsequent result tables.

#### 5.1 Heavy-lon Radiation

differs slightly from the  $\Phi$ FI experiments for which faults are injected until the injected node (NUT) fails. Indeed, this is not a feasible solution for SWIFI: Faults are likely to be overwritten before being activated or to be injected at locations that are not executed. In such cases, the NUT would continue operation infinitely. Accordingly, a timeout mechanism has been implemented in order to shut down the NUT after a prespecified time interval.

#### 5 **RESULTS OBTAINED WITH EACH FAULT INJECTION TECHNIQUE**

Three combinations of the end-to-end EDMs were used for the four fault injection techniques considered, which led to the following three experimental configurations (see also Table 2):

- NOAM: no application level mechanisms, i.e., single execution and no checksums,

- SEMC: single execution, message checksums,

- DEMC: double execution, message checksums.

In addition, a fourth configuration TEMC (triple execution, message checksums) was used in the heavy-ion experiments (see Section 5.1).

In the following paragraphs, we present in sequence the results obtained by the application of each technique. Then, these results are discussed in a subsequent paragraph. These results are further analyzed in the next section to support the analysis of the fault injection techniques. For the sake of readability of the results, Table 3 provides an Two circuits in the NUT were irradiated in separate experiments: the CPU of the application unit and the CPU of the communication unit. Because the irradiated ICs were CMOS circuits, they had to be protected from heavy-ion induced latch-up.<sup>4</sup> The triggering of a latch-up is indicated by a drastic increase in the current drawn by the circuit. To prevent latch-ups from causing permanent damage to the ICs, a special device was used to turn off the power to the ICs when the current exceeded a threshold value.

Table 4 shows the distribution of error detections among the various EDMs for each of the irradiated CPUs, and the four combinations given in Table 2 (see also for the explanations of the entries). Table 4a gathers the results for the unit that contained the fault injected circuit. Table 4b complements these results with the error data reported by the other (fault free) unit of the NUT; these data detail the percentage reported by the "Other unit" category of Table 4a.

The hardware EDMs, in particular the CPU mechanisms, detected most of the errors. This is not surprising since the faults were injected into the CPU. The proportion of errors detected by the hardware EDMs is larger for faults injected into the communication CPU than for faults injected into the application CPU. In particular, the coverage of the NMI EDMs is higher in the former case. Unexpected exceptions occur with a frequency of about 15 percent in all combinations.

4. A latch-up is the triggering of a parasitic four layer switch (npnp or pnpn) acting as a silicon controlled rectifer (SCR), which may destroy the circuit due to excessive heat dissipation.

TABLE 4 Results for Heavy-Ion Radiation: (a) Detection by the EDMs of the Unit to Which the Faulted ICs Belong;

|                  | Error          |        | App   | lication | unit (A | U) CPI | J irradi | ated   |       | Communication unit (CU) CPU irradiated |       |        |       |        |       |  |

|------------------|----------------|--------|-------|----------|---------|--------|----------|--------|-------|----------------------------------------|-------|--------|-------|--------|-------|--|

| De               | etection       | NO     | AM    | SE       | MC      | DE     | MC       | TE     | МС    | NO                                     | AM    | SE     | MC    | DE     | MC    |  |

| Mechanisms       |                | Errors | %     | Errors   | %       | Errors | %        | Errors | %     | Errors                                 | %     | Errors | %     | Errors | %     |  |

| Hardware         | CPU            | 3735   | 47.7% | 1410     | 49.0%   | 4280   | 47.4%    | 2573   | 51.3% | 1113                                   | 44.9% | 1270   | 43.2% | 1056   | 43.3% |  |

|                  | UEE            | 1173   | 15.0% | 459      | 16.0%   | 1373   | 15.2%    | 736    | 14.7% | 361                                    | 14.6% | 416    | 14.1% | 326    | 13.4% |  |

|                  | NMI            | 549    | 7.0%  | 173      | 6.0%    | 570    | 6.3%     | 286    | 5.7%  | 500                                    | 20.2% | 578    | 19.6% | 484    | 19.9% |  |

|                  | Subtotal       | 5457   | 69.7% | 2042     | 71.0%   | 6223   | 68.9%    | 3595   | 71.7% | 1974                                   | 79.6% | 2264   | 76.9% | 1866   | 76.6% |  |

| System           | OS             | 610    | 7.8%  | 222      | 7.7%    | 687    | 7.6%     | 273    | 5.4%  | 90                                     | 3.6%  | 144    | 4.9%  | 128    | 5.3%  |  |

| S                | CGRTA          | 75     | 1.0%  | 3        | 0.1%    | 30     | 0.3%     | 37     | 0.7%  | 10                                     | 0.4%  | 7      | 0.2%  | 13     | 0.5%  |  |

|                  | Subtotal       | 685    | 8.8%  | 225      | 7.8%    | 717    | 7.9%     | 310    | 6.2%  | 100                                    | 4.0%  | 151    | 5.1%  | 141    | 5.8%  |  |

| End-to           | Double exec.   | -      | -     | -        | -       | 75     | 0.8%     | 56     | 1.1%  | -                                      | -     | -      | -     | 11     | 0.5%  |  |

| end              | Checksum       | -      | _     | 70       | 2.4%    | 247    | 2.7%     | 231    | 4.6%  | _                                      | -     | 48     | 1.6%  | 75     | 3.1%  |  |

|                  | Subtotal       | -      | —     | 70       | 2.4%    | 322    | 3.6%     | 287    | 5.7%  |                                        | -     | 48     | 1.6%  | 86     | 3.5%  |  |

| Other            | Other unit     | 1095   | 14.0% | 381      | 13.2%   | 1295   | 14.3%    | 566    | 11.3% | 342                                    | 13.8% | 407    | 13.8% | 293    | 12.0% |  |

|                  | No error info. | 402    | 5.1%  | 122      | 4.2%    | 431    | 4.8%     | 216    | 4.3%  | 62                                     | 2.5%  | 73     | 2.5%  | 51     | 2.1%  |  |

|                  | Subtotal       | 1497   | 19.1% | 503      | 17.5%   | 1726   | 19.1%    | 782    | 15.6% | 404                                    | 16.3% | 480    | 16.3% | 344    | 14.1% |  |

| Triple execution |                | -      | -     | _        | -       | -      | -        | 42     | 0.8%  | -                                      |       | -      | -     | -      | -     |  |

| Fail silence     | e violations   | 186    | 2.4%  | 37       | 1.3%    | 48     | 0.5%     | 0      | 0%    | 1                                      | <0.1% | 0      | 0%    | 0      | 0%    |  |

| Total numi       | ber of errors  | 7825   | 100%  | 2877     | 100%    | 9036   | 100%     | 5016   | 100%  | 2479                                   | 100%  | 2943   | 100%  | 2437   | 100%  |  |

(b) Detection by the EDMs of the Other Unit (Detail of "Other Unit" in (a))

(a)

|            | Error        |        | AU CF | PU irrac | liated ( | Detecti | on by t | ne CU) |      | CU CPU irradiated (Detection by the AU) |      |        |      |        |       |  |

|------------|--------------|--------|-------|----------|----------|---------|---------|--------|------|-----------------------------------------|------|--------|------|--------|-------|--|

| De         | etection     | NOAM   |       | SE       | SEMC     |         | MC      | TE     | MC   | NO                                      | AM   | SE     | MC   | DE     | MC    |  |

| Mechanisms |              | Errors | %     | Errors   | %        | Errors  | %       | Errors | %    | Errors                                  | %    | Errors | %    | Errors | %     |  |

| Hardware   | CPU          | 0      | 0%    | 0        | 0%       | 0       | 0%      | 0      | 0%   | 0                                       | 0%   | 0      | 0%   | 0      | 0%    |  |

|            | UEE          | 3      | <0.1% | 2        | 0.1%     | 0       | 0%      | 3      | 0.1% | 0                                       | 0%   | 0      | 0%   | 1      | <0.1% |  |

|            | NMI          | 199    | 2.5%  | 58       | 2.0%     | 243     | 2.7%    | 103    | 2.1% | 118                                     | 4.7% | 147    | 5.0% | 103    | 4.2%  |  |

|            | Subtotal     | 202    | 2.6%  | 60       | 2.1%     | 243     | 2.7%    | 106    | 2.1% | 118                                     | 4.7% | 147    | 5.0% | 104    | 4.3%  |  |

| System     | OS           | 893    | 11.4% | 321      | 11.2%    | 1052    | 11.6%   | 460    | 9.2% | 224                                     | 8.9% | 260    | 8.8% | 189    | 7.8%  |  |

| software   | CGRTA        | 0      | 0%    | 0        | 0%       | 0       | 0%      | 0      | 0%   | 0                                       | 0%   | 0      | 0%   | 0      | 0%    |  |

|            | Subtotal     | 893    | 11.4% | 321      | 11.2%    | 1052    | 11.6%   | 460    | 0.2% | 224                                     | 8.9% | 260    | 8.8% | 189    | 7.8%  |  |

| End-to     | Double exec. | -      |       |          |          | 0       | 0%      | 0      | 0%   |                                         | -    |        |      | 0      | 0%    |  |

| end        | Checksum     |        | _     | 0        | 0%       | 0       | 0%      | 0      | 0%   | -                                       | -    | 0      | 0%   | 0      | 0%    |  |

|            | Subtotal     |        | _     | 0        | 0%       | 0       | 0%      | 0      | 0%   | _                                       | -    | 0      | 0%   | 0      | 0%    |  |

(b)

Errors detected by the Operating System (OS) mechanisms dominate the "System software" EDMs, while detection by the message checksums dominate the "End-to-end" EDMs.

Percentages for fail silence violations were between 2.4 percent and 0.5 percent for the NOAM, SEMC, and DEMC combinations when faults were injected into the application CPU. As expected, the number of fail silence violations is lower for SEMC than for NOAM and even lower for DEMC. Moreover, when faults were injected into the communication CPU, one single fail silence violation was observed (for NOAM).

The percentage of fail silence violations (0.5 percent) observed for the DEMC combination was unexpected. In principle, all effects of transient faults should be masked by the double execution of tasks. One hypothesis for explaining these violations is that, despite the specific protection device used, an undetected latch-up caused the same incorrect result to be produced by both executions of the control task. To further investigate this hypothesis, experiments were carried out with the TEMC combination that used a third time-redundant execution of the control task which was provided with fixed input data for which the results were known. This made it possible to detect errors by comparing the produced results with the correct results. This mechanism, which can be viewed as an online test program, would detect any semipermanent fault such as the

one suggested by the latch-up hypothesis. The results show that no fail silence violations occurred for the TEMC combination. As Table 4a shows, 0.8 percent of the errors were detected by the third execution of the control task. This result comes in support of the latch-up hypothesis. However, our experimental set-up does not provide sufficient observability to fully prove the latch-up hypothesis. In principle, the absence of fail silence violations could also be an effect of the change of the software configuration caused by the switch from DEMC to TEMC and the errors detected by the third execution may have been caused by regular transients. Verification of the latch-up hypothesis would require the use of a logic analyzer so that the program flow and behavior of the microprocessor could be studied in detail.

The OS and NMI EDMs dominate the detections made by the other unit of the NUT. The communication between the two units is done via two FIFO buffers (see Fig. 1) and nearly all of these detections are made by EDMs signaling empty FIFO. (An empty FIFO can be detected both by the executive software and the special NMI mechanism.)

#### 5.2 Pin-Level Injection

The forcing technique was used for the experiments carried out on the MARS system. The main characteristics of the injected faults are listed hereafter:

|             | Error          |        | Cs of th | ne appli | cation u | unit (AU | )     | IC     | s of the | commu  | inication | n unit (C | CU)   |

|-------------|----------------|--------|----------|----------|----------|----------|-------|--------|----------|--------|-----------|-----------|-------|

| De          | etection       | NC     | MAQ      | SE       | MC       | DE       | MC    | NO     | AM       | SE     | МС        | DE        | MC    |

| Med         | chanisms       | Errors | %        | Errors   | %        | Errors   | %     | Errors | %        | Errors | %         | Errors    | %     |

| Hardware    | CPU            | 71     | 11.2%    | 53       | 9.0%     | 38       | 7.0%  | 37     | 6.9%     | 37     | 8.2%      | 20        | 3.9%  |

|             | UEE            | 48     | 7.6%     | 59       | 10.0%    | 41       | 7.6%  | 113    | 21.2%    | 73     | 16.2%     | 103       | 19.8% |

|             | NMI            | 474    | 75.0%    | 430      | 73.0%    | 423      | 78.2% | 265    | 49.7%    | 260    | 57.5%     | 263       | 50.7% |

|             | Subtotal       | 593    | 93.8%    | 542      | 92.0%    | 502      | 92.8% | 415    | 77.9%    | 370    | 81.9%     | 386       | 74.4% |

| System      | OS             | 6      | 0.9%     | 6        | 1.0%     | 7        | 1.3%  | 35     | 6.6%     | 21     | 4.6%      | 30        | 5.8%  |

| software    | CGRTA          | 0      | 0%       | 1        | 0.2%     | 0        | 0%    | 0      | 0%       | 0      | 0%        | 0         | 0%    |

|             | Subtotal       | 6      | 0.9%     | 7        | 1.2%     | 7        | 1.3%  | 35     | 6.6%     | 21     | 4.6%      | 30        | 5.8%  |

| End-to      | Double exec.   | -      | -        | —        | -        | 0        | 0%    | -      | —        | _      | _         | 0         | 0%    |

| end         | Checksum       | -      | -        | 0        | 0%       | 0        | 0%    | _      |          | 1      | 0.2%      | 5         | 1.0%  |

|             | Subtotal       | -      |          | 0        | 0%       | 0        | 0%    | _      | _        | 1      | 0.2%      | 5         | 1.0%  |

| Other       | Other unit     | 1      | 0.2%     | 8        | 1.4%     | 2        | 0.4%  | 23     | 4.3%     | 17     | 3.8%      | 26        | 5.0%  |

|             | No error info. | 32     | 5.1%     | 30       | 5.1%     | 30       | 5.5%  | 59     | 11.1%    | 43     | 9.5%      | 72        | 13.9% |

|             | Subtotal       | 33     | 5.2%     | 38       | 6.5%     | 32       | 5.9%  | 82     | 15.4%    | 60     | 13.3%     | 98        | 18.9% |

| Fail silenc | e violations   | 0      | 0%       | 2        | 0.3%     | 0        | 0%    | 1      | 0.2%     | 0      | 0%        | 0         | 0%    |

| Total num   | ber of errors  | 632    | 100%     | 589      | 100%     | 541      | 100%  | 533    | 100%     | 452    | 100%      | 519       | 100%  |

| 1 | ۰. |   | ١. |  |

|---|----|---|----|--|

| ( | ć  | 1 | )  |  |

|          | Error        | ICs      | of the | AU (De | tection | by the 0 | CU)  | ICs    | of the | CU (De | tection | by the A | AU)  |

|----------|--------------|----------|--------|--------|---------|----------|------|--------|--------|--------|---------|----------|------|

| De       | etection     | NO       | AM     | SEMC   |         | DEMC     |      | NO     | AM     | SE     | MC      | DE       | MC   |

| Med      | chanisms     | Errors   | %      | Errors | %       | Errors   | %    | Errors | %      | Errors | %       | Errors   | %    |

| Hardware | CPU          | 0        | 0%     | 0      | 0%      | 0        | 0%   | 0      | 0%     | 0      | 0%      | 0        | 0%   |

|          | UEE          | 0        | 0%     | 0      | 0%      | 0        | 0%   | 0      | 0%     | 0      | 0%      | 2        | 0.4% |

| -        | NMI          | 1        | 0.2%   | 7      | 1.2%    | 2        | 0.4% | 23     | 4.3%   | 17     | 3.8%    | 24       | 4.6% |

|          | Subtotal     | 1        | 0.2%   | 7      | 1.2%    | 2        | 0.4% | 23     | 4.3%   | 17     | 3.8%    | 26       | 5.0% |

| System   | OS           | 0        | 0%     | 1      | 0.2%    | 0        | 0%   | 0      | 0%     | 0      | 0%      | 0        | 0%   |

| software | CGRTA        | 0        | 0%     | 0      | 0%      | 0        | 0%   | 0      | 0%     | 0      | 0%      | 0        | 0%   |

|          | Subtotal     | 0        | 0%     | 1      | 0.2%    | 0        | 0%   | 0      | 0%     | 0      | 0%      | 0        | 0%   |

| End-to   | Double exec. | -        | _      | -      | —       | 0        | 0%   | _      | _      | -      | _       | 0        | 0%   |

| end      | Checksum     | -        | -      | 0      | 0%      | 0        | 0%   | —      | _      | 0      | 0%      | 0        | 0%   |

|          | Subtotal     | <u> </u> |        | 0      | 0%      | 0        | 0%   | _      | _      | 0      | 0%      | 0        | 0%   |

(b)

- One single IC was fault injected at a time (the maximum number of pins faulted simultaneously—i.e., the multiplicity of the fault—being limited to mx = 3),

- Uniform distribution over all combinations of *mx* pins out of the *n* functional pins of the target IC was used to select the *mx* faulted pins,

- Stuck-at-0 and -1 fault models (all 0-1 combinations of *mx* pins were considered equally probable),

- To facilitate the comparison with the other techniques, both transient and intermittent (series of transients) faults were injected.

As a consequence of the application of the pin-forcing technique, it can be confidently considered that all pins of the ICs connected to an actually injected pin are equally faulted. Accordingly, to simplify the accessibility to the pins of the CPUs of the application and communication units, the target ICs were mainly buffer ICs connected to them. As a result, seven ICs (five on the application unit and two on the communication unit) were tested. These tests resulted in 3,266 error reports.

Table 5 shows the distribution of the errors detected by the various EDMs, together with their percentage of the total number of errors observed in each experimental configuration.

The results in Table 5a indicate a dominant proportion of detections by the hardware EDMs (more than 90 percent on the application unit side and 75 percent on the communication unit side). NMIs clearly dominate; however, in addition to CPU exceptions, a significant number of UEEs were also triggered. The difference between UEE and NMI for the application and communication units can be explained by the fact that not all ICs tested on the application unit are directly connected to the processor. In the "System software" category, the OS EDMs significantly dominate. Concerning the "End-to-end" level, the "Checksum" detections significantly dominate: No detections were triggered by the "Double execution" when this option was enabled. Only a limited number of fail silence violations were observed: two occurrences for the SEMC combination when injecting on the application unit and one occurrence for the NOAM combination when injection targeted the communication unit.

Table 5b shows that NMI EDMs also dominate the supplementary detections observed on the other unit. A significant difference is observed between the results of whether the injection affects the application unit or the communication unit; this may indicate that a larger proportion of errors was propagated to the application unit.

TABLE 6

Results for Electromagnetic Interferences: (a) Detection by the EDMs of the Unit to Which the Faulted ICs Belong;

(b) Detection by the EDMs of the Other Unit (Detail of "Other Unit" Entry in (a))

|             | Error          |        | Inje  | ction wi | th anter | nnas   |       |        | Injec | tion wit | h probe | only   |       |

|-------------|----------------|--------|-------|----------|----------|--------|-------|--------|-------|----------|---------|--------|-------|

| De          | etection       | NOA    | M(1)  | SEM      | IC(2)    | DEN    | C(3)  | NOA    | M(4)  | SEM      | 1C(5)   | DEM    | IC(6) |

| Med         | chanisms       | Errors | %     | Errors   | %        | Errors | %     | Errors | %     | Errors   | %       | Errors | %     |

| Hardware    | CPU            | 1195   | 72.0% | 193      | 76.6%    | 137    | 2.2%  | 4933   | 99.4% | 1692     | 98.1%   | 1911   | 99.2% |

|             | UEE            | 11     | 0.7%  | 8        | 3.2%     | 9      | 0.2%  | 31     | 0.6%  | 17       | 1.0%    | 15     | 0.8%  |

|             | NMI            | 48     | 2.9%  | 18       | 7.1%     | 695    | 11.4% | 0      | 0%    | 3        | 0.2%    | 0      | 0%    |

|             | Subtotal       | 1254   | 75.6% | 219      | 86.9%    | 841    | 13.8% | 4964   | 100%  | 1712     | 99.3%   | 1926   | 100%  |

| System      | OS             | 110    | 6.6%  | 5        | 2.0%     | 5215   | 85.6% | 0      | 0%    | 3        | 0.2%    | 0      | 0%    |

| software    | CGRTA          | 5      | 0.3%  | 0        | 0%       | 1      | <0.1% | 0      | 0%    | 0        | 0%      | 0      | 0%    |

|             | Subtotal       | 115    | 6.9%  | 5        | 2.0%     | 5216   | 85.6% | 0      | 0%    | 3        | 0.2%    | 0      | 0%    |

| End-to      | Double exec.   |        | -     | -        | -        | 9      | 0.2%  | -      | -     | -        | -       | 0      | 0%    |

| end         | Checksum       | -      | -     | 1        | 0.4%     | 8      | 0.1%  | -      | -     | 1        | <0.1%   | 0      | 0%    |

|             | Subtotal       | -      | -     | 1        | 0.4%     | 17     | 0.3%  | -      | -     | 1        | <0.1%   | 0      | 0%    |

| Other       | Other unit     | -      | -     | 24       | 9.5%     | 6      | 0.1%  | 0      | 0%    | 6        | 0.3%    | 0      | 0%    |

|             | No error info. | 271    | 16.3% | 0        | 0%       | 13     | 0.2%  | 0      | 0%    | 2        | 0.1%    | 0      | 0%    |

|             | Subtotal       | 271    | 16.3% | 24       | 9.5%     | 19     | 0.3%  | 0      | 0%    | 8        | 0.4%    | 0      | 0%    |

| Fail silenc | e violations   | 20     | 1.2%  | 3        | 1.2%     | 0      | 0%    | 0      | 0%    | 0        | 0%      | 0      | 0%    |

| Total num   | ber of errors  | 1660   | 100%  | 252      | 100%     | 6093   | 100%  | 4964   | 100%  | 1724     | 100%    | 1926   | 100%  |

(a)

|          | Error        |         | Inje | ection with | th anter | nnas   |         |        | Injed   | ction wit | h probe | only   |      |

|----------|--------------|---------|------|-------------|----------|--------|---------|--------|---------|-----------|---------|--------|------|

| De       | etection     | NOAM(1) |      | SEM         | SEMC(2)  |        | DEMC(3) |        | NOAM(4) |           | IC(5)   | DEM    | C(6) |

| Med      | chanisms     | Errors  | %    | Errors      | %        | Errors | %       | Errors | %       | Errors    | %       | Errors | %    |

| Hardware | CPU          | -       | -    | 0           | 0%       | 0      | 0%      | 0      | 0%      | 0         | 0%      | 0      | 0%   |

|          | UEE          | -       | -    | 0           | 0%       | 0      | 0%      | 0      | 0%      | 0         | 0%      | 0      | 0%   |

|          | NMI          | -       | -    | 0           | 0%       | 6      | 0.1%    | 0      | 0%      | 0         | 0%      | 0      | 0%   |

|          | Subtotal     | -       | -    | 0           | 0%       | 6      | 0.1%    | 0      | 0%      | 0         | 0%      | 0      | 0%   |

| System   | OS           | -       | -    | 24          | 9.5%     | 0      | 0%      | 0      | 0%      | 6         | 0.3%    | 0      | 0%   |

| software | CGRTA        |         | -    | 0           | 0%       | 0      | 0%      | 0      | 0%      | 0         | 0%      | 0      | 0%   |

|          | Subtotal     | -       | -    | 24          | 9.5%     | 0      | 0%      | 0      | 0%      | 6         | 0.3%    | 0      | 0%   |

| End-to   | Double exec. | -       | -    |             | -        | 0      | 0%      | -      | -       | -         | -       | 0      | 0%   |

| end      | Checksum     | -       | -    | 0           | 0%       | 0      | 0%      | -      | -       | 0         | 0%      | 0      | 0%   |

|          | Subtotal     | -       | -    | 0           | 0%       | 0      | 0%      | -      | -       | 0         | 0%      | 0      | 0%   |

(b)

#### 5.3 Electromagnetic Interferences

Various fault injection campaigns were carried out with a variety of voltage levels, with negative or positive polarity of the bursts, and with a burst-frequency of 2.5 kHz and 10 kHz. A total number of more than 17,000 errors were observed during all campaigns conducted with the first method, i.e., when the computer board of the node under test was mounted between two plates, and more than 30,000 errors were observed using the special probe (see Section 4.3). Most of the campaigns were conducted with all application level EDMs enabled.

In the first campaign of Table 6 (identified as NOAM(1)), faults were injected into the communication unit using the two plates. Antenna wires were attached to the so-called LO-EPROM in order to disturb the address bus and the eight low order bits of the data bus. Bursts characterized by a frequency of 2.5 kHz, negative polarity, and a voltage of 230 V were injected. The second campaign (SEMC(2)) used the special probe, with antenna wires connected to the LO-EPROM in the application unit. In this case, the bursts were characterized by a frequency of 10 kHz, negative polarity and a voltage of 300 V. Campaign number three (DEMC(3)) used the two plates, the bursts had a frequency of 2.5 kHz, negative polarity, and voltage of 230 V. The wires were attached to the LO-EPROM of the application unit. Campaigns 4 to 6 were only using the special probe for coupling faults into the CPU of the application unit, i.e., the probe was mounted on top of the CPU and no wires were attached to any chip. The chosen frequency for the bursts was 10 kHz and negative polarity was used for all these experiments. We used a voltage of 290 V for campaigns 4 and 6, while a slightly higher voltage, 300 V, was used for campaign 5.

Due to the large number of campaigns made, only selected campaigns are presented in Table 6, which shows the distribution of the errors detected by the various EDMs as total numbers and as percentage. Table 6a shows the errors detected by the unit where fault injection was focused to; errors detected by the other unit of the NUT are detailed in Table 6b.

Campaigns 1 and 2 show similar results, although focus of fault injection was on different units of the NUT, the communication unit for the first and the application unit for the second. Most of the errors were detected by the hardware EDMs, where the CPU EDMs clearly dominate. For the "system software" EDMs, which only detected a small fraction of the errors, the OS category dominates. The relatively high amount of occurrences of the "No error info." category for campaign 1 partly results from the fact that, for this campaign, no information about the errors detected by the application unit is available because this is a result from early experiments, where only the outputs of the

|              | Error          | 1      | njection | into th | e code : | segmer | nt    | I      | njectior | into th | e data s | segmen | t     |

|--------------|----------------|--------|----------|---------|----------|--------|-------|--------|----------|---------|----------|--------|-------|

| De           | etection       | NC     | MAQ      | SE      | MC       | DE     | МС    | NO     | MA       | SE      | MC       | DE     | MC    |

| Mec          | hanisms        | Exper. | %        | Exper.  | %        | Exper. | %     | Exper. | %        | Exper.  | %        | Exper. | %     |

| Hardware     | CPU            | 443    | 14.6%    | 769     | 25.4%    | 679    | 22.6% | 0      | 0%       | 0       | 0%       | 0      | 0%    |

|              | UEE            | 1433   | 47.4%    | 440     | 14.5%    | 732    | 24.4% | 1711   | 57.0%    | 88      | 2.5%     | 123    | 4.1%  |

|              | NMI            | 0      | 0%       | 0       | 0%       | 0      | 0%    | 0      | 0%       | 0       | 0%       | 0      | 0%    |

|              | Subtotal       | 1876   | 62.0%    | 1209    | 40.0%    | 1411   | 47.0% | 1711   | 57.0%    | 88      | 2.5%     | 123    | 4.1%  |

| System       | OS             | 3      | 0.1%     | 13      | 0.4%     | 12     | 0.4%  | 2      | 0.1%     | 0       | 0%       | 0      | 0%    |

| software     | CGRTA          | 103    | 3.4%     | 113     | 3.7%     | 87     | 2.9%  | 0      | 0%       | 0       | 0%       | 0      | 0%    |

|              | Subtotal       | 106    | 3.5%     | 126     | 4.2%     | 99     | 3.3%  | 2      | 0.1%     | 0       | 0%       | 0      | 0%    |

| End-to       | Double exec.   | 0      | 0%       | 0       | 0.0%     | 289    | 9.6%  | 0      | 0%       | 0       | 0%       | 626    | 20.9% |

| end          | Checksum       | 1      | 0.0%     | 211     | 7.0%     | 195    | 6.5%  | 0      | 0%       | 2378    | 68.0%    | 1787   | 59.5% |

|              | Subtotal       | 1      | 0.0%     | 211     | 7.0%     | 484    | 16.1% | 0      | 0%       | 2378    | 68.0%    | 2413   | 80.4% |

| Other        | Other unit     | 1      | 0.0%     | 0       | 0%       | 0      | 0%    | 0      | 0%       | 2       | 0.1%     | 1      | 0.0%  |

|              | No error info. | 8      | 0.3%     | 112     | 3.7%     | 0      | 0%    | 2      | 0.1%     | 0       | 0%       | 1      | 0.0%  |

|              | Subtotal       | 9      | 0.3%     | 112     | 3.7%     | 0      | 0%    | 2      | 0.1%     | 2       | 0.1%     | 2      | 0.1%  |

| IM Loss      |                | 0      | 0%       | 21      | 0.7%     | 0      | 0%    | 0      | 0%       | 494     | 14.1%    | 0      | 0%    |

| No Reply     | No Reply       |        | 24.1%    | 1090    | 36.0%    | 1006   | 33.5% | 1277   | 42.6%    | 534     | 15.3%    | 464    | 15.5% |

| Fail silence | e violations   | 304    | 10.1%    | 256     | 8.5%     | 0      | 0%    | 8      | 0.3%     | 0       | 0%       | 0      | 0%    |

| Total num    | ber of exp.    | 3024   | 100%     | 3025    | 100%     | 3000   | 100%  | 3000   | 100%     | 3496    | 100%     | 3002   | 100%  |

TABLE 7 Results for Software-Implemented Fault Injection

unit under test were recorded and, therefore, all errors that were detected by the application unit are counted as "No error info.".

A singular distribution of error reports was observed for campaign 3. There, the system software EDMs (especially OS) detected most of the errors. Most reports pointed out that a message which was required by the application was lost. Although both campaigns 1 and 3 used the "two metal plates" technique, the observed results are quite different. Conversely, while campaigns 1 and 2 had different EI conditions, the results observed are very similar. This observation and the unique feature of the results obtained during campaign 3 led us to consider them suspiciously. More generally, significantly different results were observed for similar conditions, e.g., slight changes in voltage levels. Thus, reproducibility appears to be problematic for EI experiments.

For campaigns 4 to 6, almost all of the errors were detected by the CPU EDMs. Only campaign 5 shows a small amount of errors detected by other EDMs than hardware EDMs. When looking at the results of campaigns 4 to 6 in more detail, we discovered that almost all of the detected errors were spurious interrupts detected by the CPU. Spurious interrupts are interrupts signaled to the processor, but the processor cannot find the source of the interrupt, i.e., the device having raised the interrupt. This shows that the interrupt lines of a processor are highly sensitive to EI.

For all campaigns, errors detected by the "Other unit" were only detected by the NMI EDMs and by the OS EDMs.

# 5.4 Software-Implemented Fault Injection

Both the code and data segments of the rolling-ball application software were targeted by the SWIFI technique.<sup>5</sup> Within each segment, the bit to be faulted was selected randomly to achieve a uniform distribution over the whole segment. To facilitate the comparison with the  $\Phi$ FI techniques, we only consider here the single bit-flip experiments because they constitute a reasonable fault scenario for the comparison with these techniques (e.g., heavy-ion radiation generates, to a large extent, single bit-flips).

Table 7 shows the distribution of the errors detected by the various EDMs, together with their percentage of the total number of experiments observed in each experimental configuration.

Three comments need to be made prior to analyzing these results in detail:

- 1. The bit-flips affect the code and data segments that are processed by the application unit, so the injection implicitly focuses on the application unit. The fact that the percentages observed for the "Other unit" category (i.e., the error reports returned by the communication unit) are almost negligible indicates a limited propagation of the errors.

- As opposed to  $\Phi$ FI experiments, where the experimental protocol prevented such occurrences,<sup>6</sup> a significant ratio of SWIFI experiments (up to 42 percent in the case of data segment injection) led to nonsignificant experiments where no effect could be observed (these are categorized as "NoReply" in Table 7). Such a significant proportion is a common finding in other reported work on SWIFI (e.g., see [8], [9], [11], [16], [47]). While this proportion is decreased in the case data segment injection when application-level EDMs are enabled, the opposite observation is made in the case of injection into the code segment: This can be explained by the fact that application-level EDMS are introducing additional code for implementing the checks that result in an increase in the number of potential unused areas. Nevertheless, these results exemplify the real benefits that one can expect from applying such EDMs to protect with respect to data errors.

<sup>5.</sup> To carry out a fair comparison with the  $\Phi$ FI experiments, only the results obtained while executing the rolling ball application are considered here (see [28] for more results on the SWIFI experiments).

<sup>6.</sup> Remember that the  $\Phi$ FI fault injection experiments were carried out until the NUT failed. This is not a feasible solution for SWIFI (e.g., faults can be injected at locations that are not reached by the execution process or errors can be overwritten before being propagated).

3. Another singular behavior was the intermittent omission of application messages ("IM Loss" category). Such a singular behavior was quite significant in the case of data segment injection (14 percent)! Analysis of the cause was traced to the mutilation of the time-stamp information incorporated into the end-to-end CRC (see [29] for more details).

The first observation is that the behaviors highly depend on the type of segment targeted by fault injection. While the proportion of hardware error detections dominates in the case of code segment injection, this is no longer the case for data segment injection experiments: On the contrary, endto-end EDMs significantly dominate. Moreover, especially in the NOAM configuration, the type of hardware EDMs exercised highly depend on the type of segment targeted by fault injection: While CPU EDMs were exercised frequently in the case of code segment injection, only UEEs have been observed for data segment injection.

Another interesting difference between the target segments concerns the system software EDMs: Indeed, as could be expected, these do not contribute (nearly at all) to the detection in the case of data segment injection. Also, occurrences of fail silence violations were significantly higher for code segment injection. However, in both cases, the utilization of end-to-end EDMs (especially, double execution<sup>7</sup>) in addition to hardware and system software EDMs proved useful to eliminate this risk.

### 5.5 Discussion

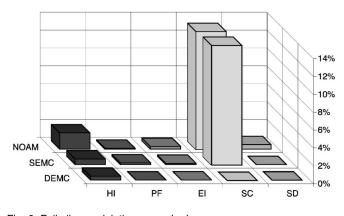

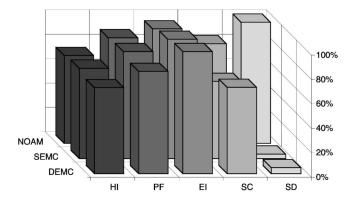

We synthesize here the results related to the evaluation of the efficiency of the various EDMs implemented in the MARS architecture. In particular, these results provide objective insights to the designers in getting confidence in the way the fail silence property of the computing nodes has been achieved. The analysis focuses on the complementarity of the EDMs in contributing to the fail silence property. The detailed analysis of the different erroneous behaviors provoked by the fault injection techniques considered is presented in Section 6.

Most  $\Phi$ FI fault injection campaigns show that the hardware EDMs significantly detect most of the errors.<sup>8</sup> Conversely, the impact of hardware EDMs is much less important in the case of the SWIFI experiments. Furthermore, the target segment (code or data) has a dramatic impact on the type of mechanisms exercised (and thus on the type of errors generated). Accordingly, these two techniques will be considered separately in the analyses carried out in Section 6.

A closer examination of the errors detected by the hardware EDMs revealed that 5.0 percent, 11.6 percent, and 1.9 percent of the errors were detected by the time-slice controller (TSC)—that is, triggering an NMI—for heavy-ion, pin-forcing, and EI, respectively. Although no NMIs were observed during the SWIFI experiments reported here, a

small number of NMIs generated by the time-slice controller were observed during other experiments. No fail silence violations in the time domain (see Section 5.4) were observed during these experiments, thus demonstrating the usefulness of this error detection mechanism.

The *system software EDMs* detected the second largest amount of errors for all the  $\Phi$ FI techniques. The imbalance observed in the case of heavy-ion radiation between the OS and CGRTA EDMs is amplified when using pin-forcing and EI: Almost no detections by the CGRTAs were observed for the two latter techniques. For SWIFI, on the contrary, the CGRTA EDMs dominate, but the overall impact of the system software EDMs is significantly reduced.

The *application-level (end-to-end) EDMs* detected the smallest amount of errors for all  $\Phi$ FI techniques. This is opposite for the SWIFI technique. However, when these were disabled, the fail silence coverage was significantly reduced (particularly for heavy-ion radiation and SWIFI on code segment), which shows the necessity of using these mechanisms as well.

Another important outcome of the study concerned the analysis of the impact of the various EDMs on the fail silence property of a MARS node. The results shown for each technique in the previous tables, where three configurations involving, respectively, both (DEMC), only one (SEMC), or none (NOAM) of the end-to-end EDMs are presented, sustain the conviction that the end-to-end EDMs play a dominant role (with respect to the other EDMs) in achieving the fail silence property. To further check this view, a specific series of experiments was carried out for HI and PF for which the NMI EDMs were disabled. These experiments focused essentially on the application unit processor. The results can be summarized as follows: In both cases, almost no fail silence violations were observed for the DEMC configuration (with NMI disabled), while, as shown in Tables 5 and 6, the NOAM configuration (with NMI enabled) exhibited a significant number of fail silence violations.

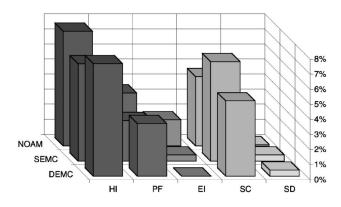

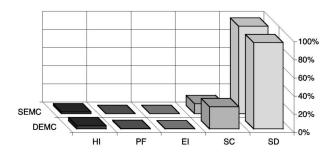

# 6 ANALYSIS OF THE FAULT INJECTION TECHNIQUES